DRAM市场在过去的一年多时间里,经历了一次过山车,从供过于求到供小于求,再到最后的供求平衡,连带着厂商的财报也做起了过山车。

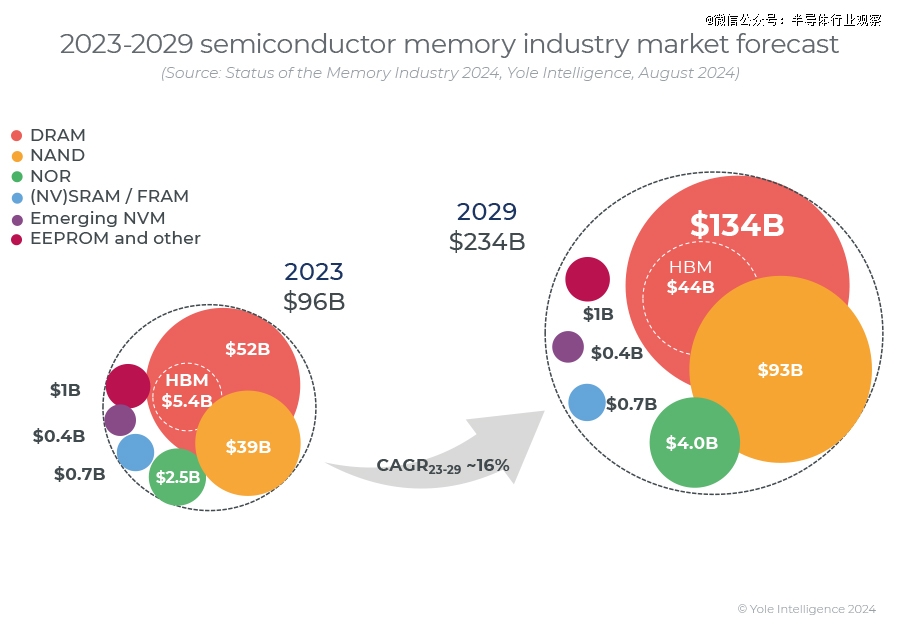

根据Yole研报,存储行业目前正在以比之前预测更快的速度复苏,收入有望在 2024 年和 2025 年飙升。在 2024 年 DRAM 收入增至 980 亿美元之后,预计 2025 年收入将继续增长至创纪录新高,DRAM 市场预计将达到 1370 亿美元,而受强劲的需求增长(尤其是数据中心领域的需求)的推动,预计DRAM市场长入将在 2029 年继续增长至 1300 亿美元,23-29 年复合年增长率约 17%。

好消息是市场正在恢复正常,坏消息是厂商又要开卷了,在市场逐步恢复正轨的过程中,各家为了拿下更多的市场份额,也使出了浑身解数,即使是在DRAM市场已经厮杀至仅余三大巨头——三星、SK海力士和美光的情况下,竞争态势依旧非常激烈。

对于半导体行业来说,永远是技术为先,谁能在技术上实现*,就能把这种优势转化到市场之中,DRAM这类产品也是如此。

其中,三星和SK海力士已经商业化了基于1a和1b芯片设计的产品,包括DDR5、LPDDR4X、LPDDR5和LPDDR5X,它们的DRAM芯片设计为最小的12nm级别。两家公司在采用EUV光刻方面处于*地位,而美光则继续使用ArF和ArFi光刻技术到1α和1β代,并计划在1γ代引入EUV。三星在1a和1b代将EUV光刻扩展到五层以上的掩模。SK海力士也采取了类似的策略,计划在未来增加EUVL步骤。

针对目前最热的HBM技术,尽管三家厂商均已官宣HBM3E,但三星是*个宣布和量产12层HBM3E的厂商,而SK海力士会在今年第三季度量产12层HBM3E,美光则会在下半年完成该产品的量产。

至于这三家厂商在DRAM技术上表现具体如何,不妨来看更详细一点的解读。

01 转向EUV

“虽然不太好,但这时候才能真正展现出实力。”2019年1月,三星电子会长李在镕在结束“2019企业家对话”后被问及半导体市场状况时这样回答。

在旁边听到这一回答的SK集团会长崔泰源说:“三星说这种话是最让人害怕的。”

李在镕所说的“真正实力”隐含了三星电子自1990年代以来在全球DRAM市场上一直保持*位置的强大实力。

1992年12月,三星首次拿下全球DRAM市场的*,而后就再未将这一位置让出过,可以说DRAM就是三星电子最粗壮的根系,源源不断为这棵参天大树供应养分。三星电子DS部门的高层人士表示:“传统上有一种不成文的规定,‘天才工程师必须去DRAM开发团队’,而领导DRAM开发和设计的团队负责人都是天才中的天才。”

三星DRAM独步全球的原因很简单,就是把微缩工艺技术做到了遥遥*。DRAM微缩工艺的重要性在于它直接影响产品性能。随着电路线宽的缩小,DRAM的集成度提高,从而提升了性能和电源效率。这意味着电子设备的响应速度更快,电池消耗更少。此外,随着可以从一块晶圆上制造的半导体数量增加,生产效率也得到了提高。

DRAM微缩工艺从30纳米、20纳米逐步演进到10纳米,三星电子在此过程中一直占据压倒性优势。10纳米级DRAM按1x-1y(第二代)-1z(第三代)-1a(第四代)-1b(第五代)的顺序生产。三星早在2016年*季度就宣布率先量产10纳米级1x工艺,而SK海力士和美光则几乎晚了整整一年才开始量产,从10纳米级的1x到1z,三星都是毋庸置疑的*,从技术和市场上都对另外两家形成了碾压之势。

但是变数就出现在了第四代上。2021年1月,美光宣布率先量产10纳米级第四代DRAM,改变了过往三星具备*统治力的格局。随着DRAM进入10纳米级工艺,微缩技术难度大幅增加,过去通过改良氟化氩(ArF)光刻设备来推进的微缩工艺已达到极限,从2022年开始,大家普遍认为三星、SK海力士和美光的DRAM技术本质上已处于同一水平线上,

在氟化氩设备达到极限的现阶段,极紫外光刻设备登上了舞台,作为利用极紫外光在芯片上刻画超微细电路的下一代半导体生产设备,其被视为突破现有设备技术限制的替代方案。

在10纳米级第四代开发工艺中,三星和SK海力士率先引入了EUV光刻技术,而美光的做法稍有不同,它采用了传统光刻设备进行多次细微电路刻画的“多重图案化”技术,从而更快地实现了微缩工艺转换。尽管这种方法不需要完全改变现有方式,但由于需要多次刻画电路,也会带来工艺步骤增加,生产效率下降等问题。

三星电子在10纳米级第四代时微缩工艺转换速度变慢的原因,被分析认为是研发组织的官僚化和EUV工艺转换中的试验错误等多种因素共同作用的结果。三星电子的一位高层人士解释说:“在微缩工艺进入10纳米级时,芯片设计和生产的复杂性增加,而管理层在获得下一代技术方面显得过于自满。特别是EUV设备在优化DRAM生产上花费了相当长的时间。”

2024年,DRAM技术竞争的关键在于10纳米级第五代工艺,三星、SK海力士和美光几乎同时开始量产该工艺的产品。1b工艺的电路线宽仅为12纳米,还用于最新的HBM3E。根据三星、SK海力士、美光的工艺路线图和全球投资银行UBS的数据,三家公司计划从今年上半年开始大幅增加10纳米级第五代DRAM的生产量。

半导体行业人士认为,三家公司之间的DRAM技术竞争“真正的较量”还未开始。特别是将处理难度较高的EUV设备稳定应用于DRAM工艺中,以提升性能和生产效率,是胜负的关键。EUV光刻设备被用于10纳米级初期及更微小的第五代DRAM生产工艺中。将EUV设备应用于DRAM工艺中,可以减少复杂的生产步骤,提高效率。

三星电子和SK海力士今年的设备投资方向是向DRAM的尖端工艺转型。由于人工智能热潮带动了HBM和大容量DDR5的需求增加,扩大尖端DRAM的产量变得迫在眉睫。根据Ebest投资证券的预测,今年第四季度,1b DRAM在三星电子和SK海力士整体DRAM生产量中所占比例预计分别为13%和11%。

2021年,三星电子率先在业界将EUV光刻设备应用于DRAM生产工艺,估计已投入了数千亿韩元,利用至少30台EUV设备用于生产工艺。由于比竞争对手更早在DRAM中应用EUV光刻设备并经历了试验错误,预计从今年开始,三星将在尖端工艺转型上加速。

SK海力士也在其利川工厂安装了6到7台EUV设备,正在稳定DRAM的量产。SK海力士计划到今年年底,将10纳米第四代和第五代工艺的生产比例扩大到DRAM总产量的一半以上。尽管维持有限的设备投资规模,但为了扩大预期需求旺盛的DDR5和HBM3E等高附加值产品的生产,将集中力量推进尖端工艺的转型。

美光是最晚采用EUV设备的DRAM厂商,其在第四代和第五代10纳米DRAM上均沿用了DUV而非EUV,去年美光才宣布在广岛工厂中引入EUV光刻技术,今年其表示使用EUV光刻技术的 1γDRAM 试生产进展顺利,有望在 2025 年实现批量生产。

据韩媒报道,浦项工科大学电子电气工程系教授李炳勋表示:“未来在DRAM市场上的竞争力将由DRAM量产中引入的EUV工艺决定。随着DRAM电路设计和结构的复杂化以及工艺的微缩化,EUV工艺的重要性日益增加。那些能够迅速引进并有效利用EUV光刻设备的企业将占据DRAM市场的主导地位。”

除了EUV技术的导入外,高K金属栅极技术也变得越来越普遍。三星首次在1x GDDR6芯片的外围结构中使用HKMG,并扩展到1y DDR5芯片。美光在1z图形DRAM中实现了HKMG,并计划从1β代开始将其扩展到所有DRAM类型。SK海力士在1y和1a GDDR6中采用了HKMG,并最近在1b DDR5设备中使用了这项技术。

预计到明年年初,三大厂商将大规模量产1c DRAM,随后在2026年或2027年推出最终的10纳米DRAM产品,到2030年,DRAM技术预计将缩小到个位数纳米节点,涵盖0a、0b、0c或0α、0β、0γ等几代产品,就目前来看,三星为此正专注开发VS-CAT和VCT 3D DRAM,而SK海力士和美光则聚集于垂直堆叠DRAM。

02 决战HBM

HBM毫无疑问是过去一年多时间里最热门的DRAM技术和产品,三星、SK海力士和美光围绕着它展开了一场“三国大战”。

SK 海力士已经成为了这一行业的领头羊,正在不断巩固自己在这个利基市场的领导地位,仅今年一年,SK 海力士就向韩国国内的先进封装设施投入了 1.3 万亿韩元,以提高其生产高端芯片的能力,而据高盛表示,该公司去年占据了 HBM 市场的 54%。

海力士从第三代开始,就率先为其 HBM 配备所谓的 MR-MUF封装技术,该技术涉及在堆叠的芯片之间注入液化保护材料以保护设备并防止热量散失,被认为是 SK 海力士目前在该领域占据主导地位的核心动力。

海力士表示,其在开发第三代HBM产品——HBM2E时,将传热控制作为改进的主要焦点。即便TC-NCF技术被公认为是适用于密集堆叠产品的封装解决方案,SK海力士仍旧坚持不断挑战现状,最终于 2019年推出了新型封装技术MR-MUF。

其提到,MR-MUF技术由SK海力士多个团队共同开发,该技术能够同时对HBM产品中所有的垂直堆叠芯片进行加热和互联,比堆叠芯片后填充薄膜材料的TC-NCF技术更高效。此外,与TC-NCF技术相比,MR-MUF技术可将有效散热的热虚设凸块数量增加四倍。

作为对比,三星所选择的 TC NCF,与MR-MUF略有不同。其每次堆叠芯片时,都会在各层之间放置一层非导电粘合膜。该膜是一种聚合物材料,用于将芯片彼此隔离,并保护连接点免受冲击。这种方法的优点是可以*限度地减少随着层数增加和芯片厚度减小而可能发生的翘曲,使其更适合构建更高的堆栈。”

值得一提的是,MR-MUF技术另一个重要特性是采用了一种名为环氧树脂模塑料的保护材料,用于填充芯片间的空隙。EMC是一种热固性聚合物,具有*的机械性、电气绝缘性及耐热性,能够满足对高环境可靠性和芯片翘曲控制的需求。由于应用了MR-MUF技术, HBM2E的散热性能比上一代HBM2提高了36%。

为了保持产品的整体厚度,DRAM芯片必须比8层HBM3所用的芯片薄40%,因此解决芯片翘曲成为了一个关键问题。SK海力士为此开发了更加先进的MR-MUF技术,并引入了业界首创的芯片控制技术和改善散热效果的新型保护材料。在此过程中,因其在先进MR-MUF技术中应用的新型EMC与原始MR-MUF技术中的EMC相比,使散热性能提高了1.6倍。

讲完了海力士,再来说说美光。去年还处于落后状态的美光在今年实现了弯道超车,打破了三星电子和SK海力士的双雄格局,正式加入到这场竞争中,自今年第二季度起,美光已经开始向其*客户——英伟达提供少量HBM,从而形成了三强争夺的局面。

据悉,SK海力士是三家公司中最早通过英伟达质量测试的公司,成为了英伟达的主要供应商,业界估计,SK海力士的HBM3E良率已进入稳定阶段,其营业利润率大约是DRAM的两倍。

但SK海力士在短期内扩大HBM3E的生产能力仍面临挑战。知情人士透露,尽管英伟达持续向SK海力士施压,要求增加供应量,但SK海力士除了生产HBM3E,还需生产现有的HBM3,因此其可用生产能力实际上已达到极限。

另一方面,美光虽然已经开始向英伟达供货,但由于良率问题,目前只能少量供应。根据美光公布的财报细节显示,该公司在过去三个月内向英伟达供应了价值约1亿美元的HBM3E产品,而考虑到HBM3E的单价,这一供应量并不算大规模供应。

业界推测,美光在良率方面也遇到了困难。根据美光公开的资料,HBM业务的营业利润率不及DRAM。通常情况下,HBM的价格是DRAM的2-3倍,这意味着美光尚未在HBM业务中实现理想的盈利能力。

消息人士表示:“考虑到美光自信地提及将在明年大规模量产和供应HBM3E,因此预计今年内HBM3E的供应量不会有显著增加。英伟达方面则必须加快三星电子HBM3E的质量认证,并获取供应,以满足AI加速器的销售需求。”

三星明显落后于上述两家厂商,其向英伟达供应HBM3E的进程出现了延迟,原因很简单,它所开发的全球*36GB容量的12层HBM3E产品,截止目前仍未通过英伟达的质量测试。据悉,HBM质量认证通常需要超过1000小时的测试,通过测试后,双方才会进入正式合同程序。

据称,尽管三星电子的HBM3E产品是业界*实现12层结构的产品,但在性能与能耗比方面尚未达到英伟达的标准。有传闻显示,英伟达已要求三星电子对HBM3E的部分设计进行修改,三星电子也已投入大量设计和工艺人员以解决这一问题。如果三星电子的HBM3E 12层产品获得英伟达的批准,HBM业务有望在今年下半年至明年上半年进入正轨。

另外值得关注的是,SK海力士和美光都已经用上第五代10nm即1b工艺,但是三星目前仍然相当依赖第四代10nm(14nm)即1a工艺,这很有可能是其迟迟解决不了HBM散热问题的主要原因之一。

除了上述已有制造工艺和封装技术的改进外,混合键合也成为了HBM战场中的焦点。

据业内人士透露,SK海力士正在开发计划于明年量产的HBM4产品,并采用两种不同的结合方式:现有的“MR-MUF”和混合键合技术。

键合指的是半导体之间的粘合工艺。HBM是一种通过堆叠DRAM制成的产品,而MR-MUF键合方式则是在先加热进行类似焊接的操作后,再在芯片之间注入粘性液体,使其硬化,同时进行芯片保护外壳的“成型”工艺。在这个过程中,DRAM之间通过称为“凸点”的材料连接。而混合键合技术则是在没有凸点的情况下直接连接DRAM。这种技术可以显著减少HBM的厚度,并缩短DRAM之间的距离,从而加快数据传输速度。由于这种技术弥补了现有结合方式的不足,因此受到主要客户的高度关注。

半导体行业的一位人士表示:“由于混合键合的技术难度较高,SK海力士可能会在HBM4的16层产品中继续使用MR-MUF,但预计从后年开始,SK海力士将无论如何都会引入混合键合技术。”

需要注意的是,国际半导体标准化组织最近将HBM4的厚度标准从上一代的720微米(?)放宽至775微米。按此标准,内存企业可以有更大的余地使用现有的键合方式来制造HBM4。这意味着在未来一段时间内,MR-MUF和混合键合技术可能会并行存在。

相较于目前处在上风的海力士,较为弱势的三星对于在HBM4上成功应用混合键合技术表现出强烈的意愿。业内人士表示:“如果混合键合技术遇到困难,三星电子可能会从目前的‘TC-NCF’方式转向MR-MUF,但他们似乎更倾向于大力推进混合键合。”

三星认为,在16层以上的HBM产品中,混合键合技术是必不可少的。他们在最近于美国科罗拉多州丹佛市举行的电子元件技术会议上发表了相关论文,表达了这一立场。三星电子希望不受JEDEC厚度标准放宽的影响,通过率先成功实现混合键合技术,成为市场的*。

这也可能促使SK海力士加快混合键合技术的开发速度,以应对来自三星电子的追赶。SK集团会长崔泰源本月初访问了位于利川的SK海力士总部,并向员工传达了“要在明年尽早实现第六代HBM的商用化”的信息。业内人士认为,这一表态也包括了混合键合技术。事实上,SK海力士的高层人员在公开场合频频提及混合键合封装技术。

与此同时,作为存储器市场第三的美光也正在为HBM4进行混合键合技术的研究。然而,业内观察人士认为,美光在这方面的技术相对不如三星电子和SK海力士成熟。业内人士表示:“美光可能会在未来一段时间内继续使用目前的TC-NCF工艺。”

03 值得关注的新技术

除了传统的三大家之外,也有其他的中小型企业,正在关于DRAM新技术上下功夫。

就目前来看,大语言模型的规模和复杂性不断增长,而该类模型需要不同数量的内存来存储其参数,其对高带宽的需求正在不断变大,但在高带宽但低密度的市场中,却存在明显的空白。

一家专注于DRAM的无晶圆厂公司PieceMakers近期推出了全新的HBLL RAM,填补了这一市场空白。“HBLL RAM”这个名称代表了高带宽、低延迟和随机访问。与HBM相比,HBLL RAM具备两项额外的优势:低延迟和随机访问能力。此项创新满足了AI应用的需求,提供了低密度与高带宽的结合。

目前正在量产的HBLL RAM代产品提供了0.5GB的低密度和每秒128GB的带宽。未来的产品正在设计中,使用堆叠技术以进一步提升性能。策略包括在垂直方向上增加数据速率,并在水平方向上扩大I/O宽度。与HBM类似,HBLL RAM采用了512个I/O和1K I/O的数据传输方式,未来的产品将进一步提升频率。

将HBLL RAM与HBM进行比较时,其优势显而易见。在相同密度下,HBLL RAM提供了更高的带宽。相反,在相同带宽下,它提供了更低的密度。这一改进通过带宽密度指数得以量化,该指数衡量每单位密度的*带宽。HBLL RAM在这一指标上显著优于HBM、低功耗DDR和GDDR。

在能效方面,HBLL RAM由于其创新的低密度架构,提供了更高的功效。这种架构最早于2017年在ISSCC上首次亮相。单颗HBLL RAM芯片通过八个通道提供每秒128GB的带宽,所有信号凸点都位于芯片的一侧。该设计使得延迟大约是传统DRAM的一半,并且在随机访问带宽上表现优异。

知名行业分析师Jim Handy在一篇文章中强调了HBLL RAM的潜力,展示了它在三级缓存和DRAM之间的作用。事实上,使用HBLL RAM作为四级缓存的模拟结果令人印象深刻:延迟减半,平均带宽显著提高。

内存控制器的简单性是另一个优势,PieceMakers公司直接向客户提供该控制器。HBLL RAM的接口简单且类似SRAM,仅涉及读写操作、刷新和模式寄存器设置。PieceMakers的演示板和客户的电路板展示了这一创新,使用了仅ABF设计而没有使用CoWos技术。CoWos是一种先进封装技术,其成本可能是传统倒装芯片封装的2到3倍。展望未来,PieceMakers计划以类似于HBM的方式对HBLL RAM进行堆叠,但无需CoWos。相比2.5D封装,这种2D堆叠方法有望进一步降低成本。

除了HBM外,传统的DRAM领域也在涌现着更多创新。PieceMakers

3D NAND 闪存和 3D DRAM的开发商NEO Semiconductor在今年8月宣布了最新的3D X-AI 芯片技术,该技术旨在通过在 3D DRAM 中实现 AI 处理来取代高带宽存储器 内的现有 DRAM 芯片,以解决数据总线瓶颈问题。

NEO表示,采用NEO 3D X-AI技术的AI芯片可以实现大幅的性能加速和功耗降低,达成8倍内存密度,可以减少 AI 工作负载期间 HBM 和 GPU 之间传输的大量数据

“目前的AI芯片由于架构和技术效率低下,浪费了大量的性能和功耗。” NEO Semiconductor创始人兼首席执行官Andy Hsu表示。“目前的AI芯片架构将数据存储在HBM中,并依靠GPU执行所有计算。这种分离的数据存储和数据处理架构使数据总线成为不可避免的性能瓶颈。通过数据总线传输大量数据会导致性能受限和功耗非常高。3D X-AI可以在每个HBM芯片中执行AI处理。这可以大大减少HBM和GPU之间传输的数据,从而提高性能并大幅降低功耗。”

据了解,单个 3D X-AI 芯片包含 300 层 3D DRAM 单元,容量为 128 Gb,以及一层包含 8,000 个神经元的神经电路。据 NEO 估计,每个芯片可支持高达 10 TB/s 的 AI 处理吞吐量。使用 12 个 3D X-AI 芯片与 HBM 封装堆叠可实现 120 TB/s 的处理吞吐量,从而将性能提高 100 倍。

Network Storage Advisors 总裁 Jay Kramer表示:“3D X-AI 技术的应用可以加速新兴 AI 用例的开发,并促进新用例的产生。利用 3D X-AI 技术打造下一代优化的 AI 芯片,将为 AI 应用开启创新新时代。”

上述两家企业在DRAM上的创新只是目前技术发展的一瞥,随着AI应用的持续火热,未来也会更多公司提出自己的解决方案,有望成为DRAM技术的一个备选路线。

04 谁能笑到最后

在过去几年时间中,曾经的笑傲市场二三十年的霸主似乎不复以往的辉煌,英特尔经历了史上*裁员和股价暴跌,而三星则在HBM上举步维艰,连DRAM微缩技术也不复*。

与它们形成鲜明对比的是其他厂商,尤其是英伟达和海力士,前者依靠AI实现了3万亿美元市值,而后者则是在潜心经营多年HBM后获得了丰厚回报。

就目前来看,三星似乎已经是痛定思痛,将全部精力再度放回了DRAM上,不论是微缩工艺还是HBM,都不容有失,而海力士则是占据技术和市场上的主动权,多年屈居第二的它也想尝尝*名的味道,至于美光,尽管在近两年表现得颇为强势,但由于前几年在HMC上的误判和较慢的EUV技术导入速度,可能还需要花费相当长一段时间来追赶韩厂。

谁能在这场厮杀中脱颖而出,我们不妨拭目以待。

郑重声明:此文内容为本网站转载企业宣传资讯,目的在于传播更多信息,与本站立场无关。仅供读者参考,并请自行核实相关内容。